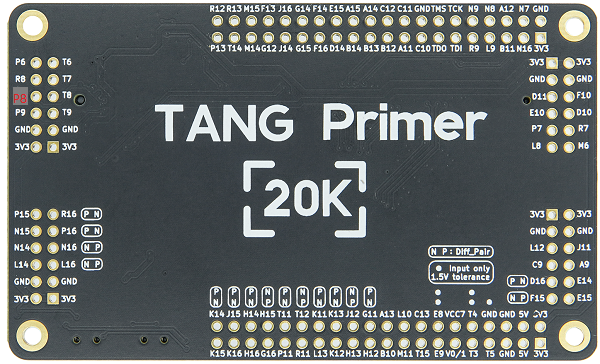

Tang Primer 20K

概述

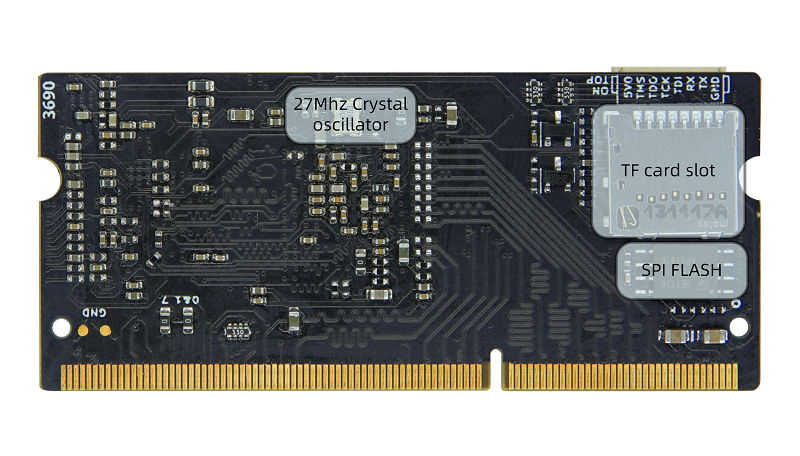

Tang Primer 20K 是基于 GW2A-LV18PG256C8/I7 所设计的一款 DDR3 sodimm 封装的核心板,额外准备了两个底板,分别为 Dock 底板和 Lite 底板。

购买链接:淘宝

基础参数

| 项目 | 参数 | 补充 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| FPGA 芯片 | GW2A-LV18PG256C8/I7 |

|

||||||||||||||||

| 内存 | 128M DDR3 | |||||||||||||||||

| Flash | 32Mbits NOR Flash | 查看 烧录到Flash | ||||||||||||||||

| 调试接口 | Jtag + Uart | JST SH1.0 8Pins 连接器 | ||||||||||||||||

| SD 卡槽 | 一个 | 推拉式 | ||||||||||||||||

| 显示接口 | 8Pins spi lcd 连接器 | |||||||||||||||||

| 整体封装 | 204P DDR3 Sodimm 金手指 | |||||||||||||||||

| 可用 IO | 一共 117 个 |

底板对比

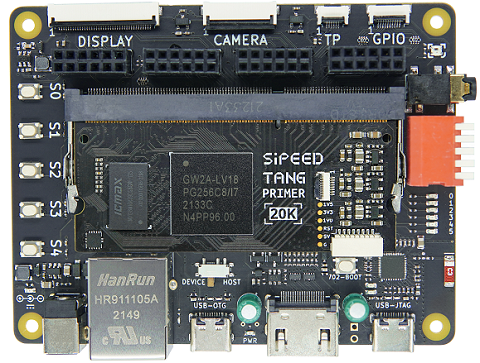

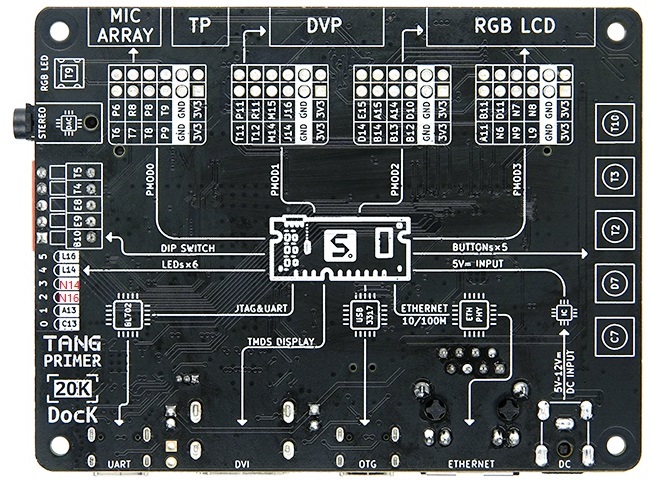

Dock 底板产品图

其中 LED2 和 LED3 所对应的引脚编号为 N16 和 N14。查阅右图左方,已标明。

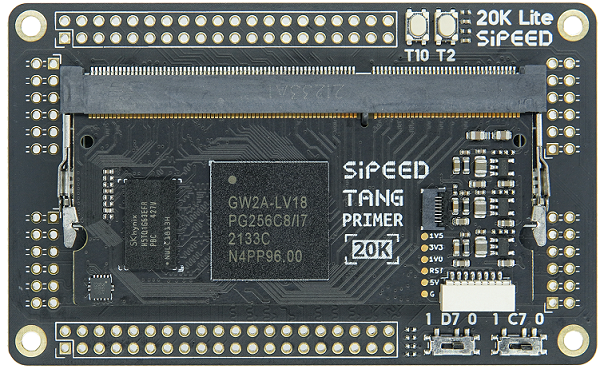

Lite 底板产品图

底板 R8 与 P9 之间为 P8 引脚。参考右图左上方,已标明

外设参数对比

| 项目 | Dock | Lite | |||

|---|---|---|---|---|---|

| 数量 | 补充说明 | 数量 | 补充说明 | ||

| RGB 接口 | 1 | RGB565 40P FPC 连接器 | |||

| DVP 接口 | 1 | 24P FPC 连接器 | |||

| 麦克风阵列接口 | 1 | 10P FPC 连接器 | |||

| 触摸接口 | 1 | 6P FPC 连接器 | |||

| PMOD 接口 | 4 | 4 | |||

| 3.5mm 耳机接口 | 1 | 使用 LPA4809MSF 驱动 | |||

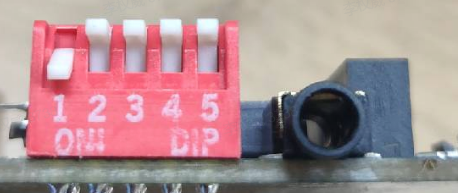

| 拨码开关 | 1 | 5P 拨码开关 | |||

| 滑动开关 | 1 | 切换板载 USB 功能 | 2 | 用户自定义功能 | |

| Type-C 接口 | USB-JTAG&UART | 1 | 板载 BL702 芯片用来 下载比特流并提供串口功能 |

||

| 自定义 USB | 1 | USB3317 芯片与滑动开关 来自定义该 USB 接口功能 |

|||

| 无线天线 | 1 | 使用 BL702 芯片的无线功能 | |||

| 按键 | 6 | 一个用来烧录 BL702, 剩下五个用户自定义功能 |

2 | ||

| LED | 6 | ||||

| HDMI 接口 | 1 | ||||

| 以太网接口 | 1 | RTL8201F 芯片实现以太网功能 | |||

| RGB LED | 1 | WS2812 | |||

硬件资料

规格书、原理图、尺寸图等均可在这里找到:点击这里

上手简明

准备开发环境 -> 学习相关语法 -> 查看开箱指南 -> 基础代码编写 -> 查看官方文档

安装 IDE :点击这里

查看 上手指南 来避免一些问题,并且从那里面可以开始进行代码实战。

如果进行完上面的点灯操作后后感觉有压力,可以自己查漏补缺:

可以在下面的这些网站学习 Verilog:- 在线免费教程:Verilog 教程(学习Verilog)

- 在线免费 FPGA 教程:Verilog (英文网站)

- Verilog 刷题网站:HDLBits(英文网站)

- 在线高云半导体可参考视频教程:点击这里

对 IDE 使用有疑问的话,可以查看官方的一些文档来熟悉相关内容

- SUG100-2.6_Gowin云源软件用户指南.pdf

- SUG949-1.1_Gowin_HDL编码风格用户指南.pdf

- UG286-1.9.1_Gowin时钟资源(Clock)用户指南.pdf

- SUG940-1.3_Gowin设计时序约束用户指南.pdf

- SUG502-1.3_Gowin_Programmer用户指南.pdf

- SUG114-2.5_Gowin在线逻辑分析仪用户指南.pdf

上面的所有文档都已经打包进了下载站点我跳转,需要的话可以点击压缩包全都下载下来。

例程汇总

公开例程

github 链接: https://github.com/sipeed/TangPrimer-20K-example

部分教程

交流方式

- 交流论坛: bbs.sipeed.com

- QQ 交流群:834585530

- 直接本页下方留言

- 商业邮箱 : support@sipeed.com

补充说明

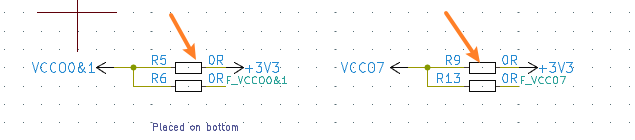

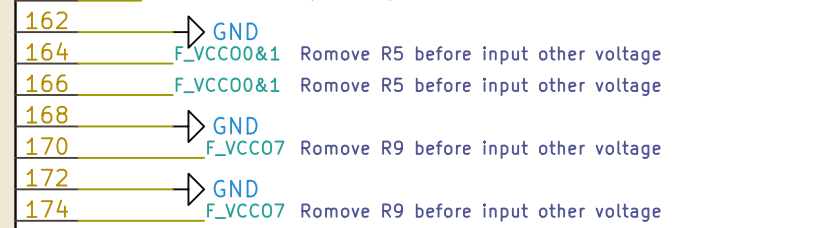

对于板子上的 bank 0、bank 1、bank 7 这 3 个 bank 电压,默认所接的是 3.3V,对应的 bank IO 会对外输出 3.3V 电压。如果需要输入自定义的 IO bank 电压,请拆除 R5 和 R9,请参考对应 Assembly 点我跳转 图来确定 R5 和 R9 的位置。

对应核心板原理图上在金手指处的说明如下

相关问题

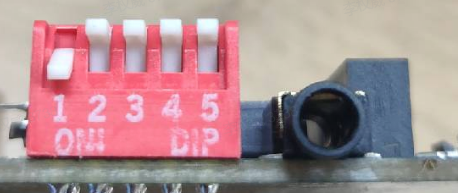

Dock 底板不工作

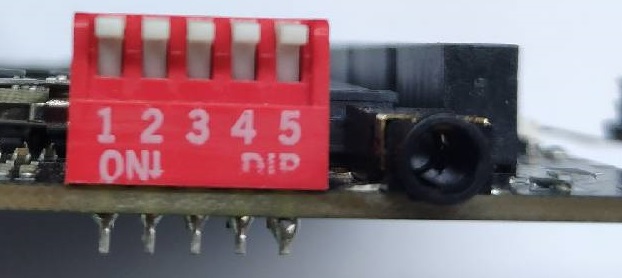

拨下 1 号拨码开关以使能核心板,不然底板会不工作且 LED0 和 LED1 常亮。

| 使能核心板 | 未使能核心板 |

|---|---|

|

|

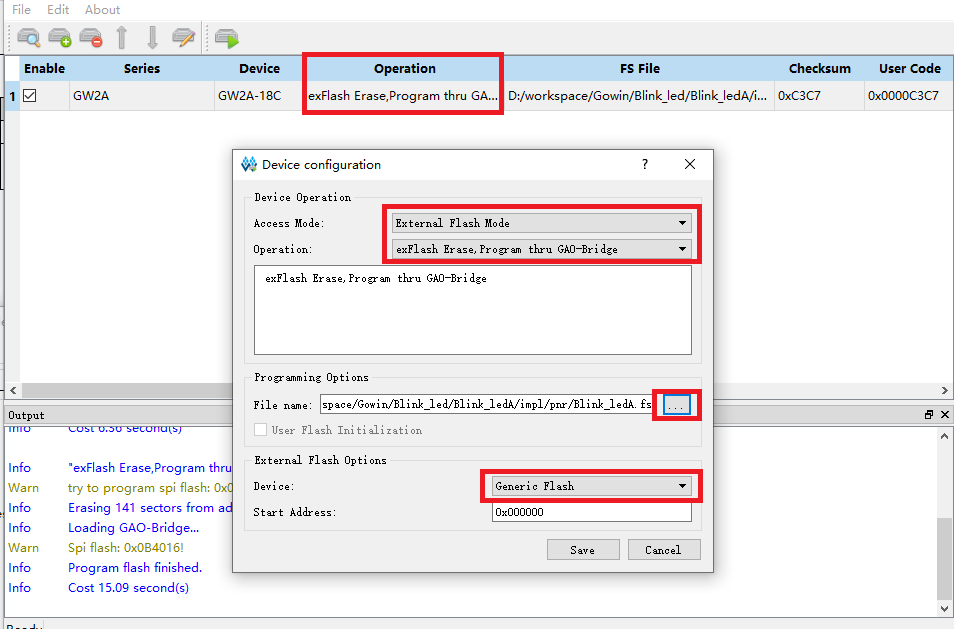

如何下载到外部 FLASH

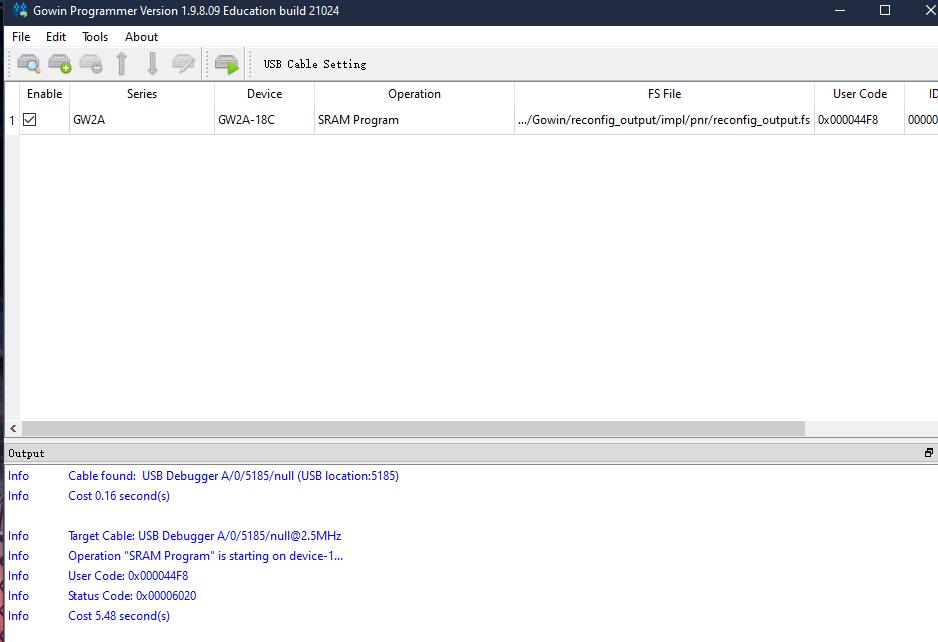

进行如下选项设置:

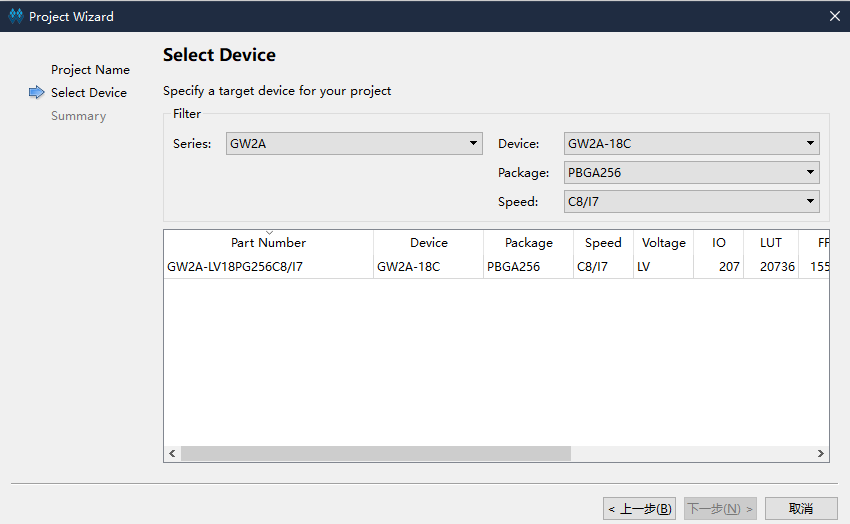

烧录后没反应或者引脚现象不对

首先确定选择了正确的型号,下图中的每一个参数都要求一致

然后检查自己的代码和对应的仿真波形是否满足要求

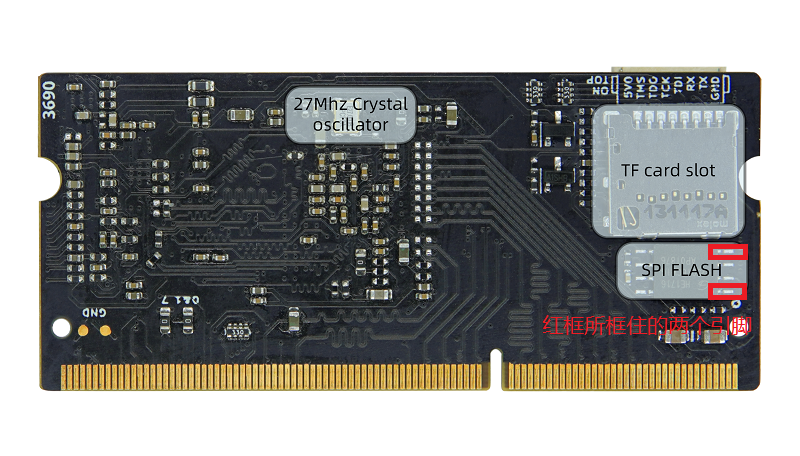

成功烧录过一次外部 Flash 后 Programmer 软件无法再烧录

注意描述是成功烧录过一次 Flash。

这种情况默认为启用了错误的引脚复用而导致下载器不能再识别到 FPGA 的 JTAG。可以短接 Flash 的 1、4 引脚,让芯片上电时不能正常读 FLASH 。

如果有 dock 底板的话,可以直接操作一号拨码开关重新救活核心板,具体操作如下:

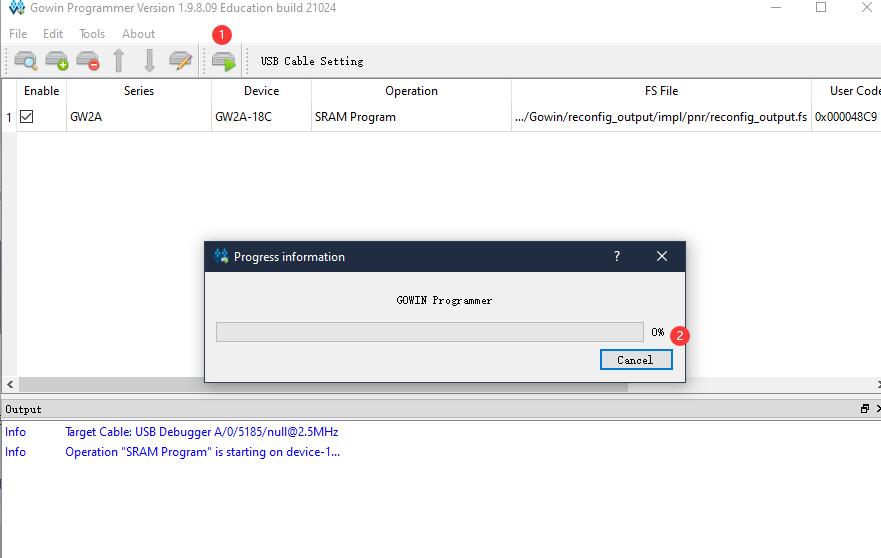

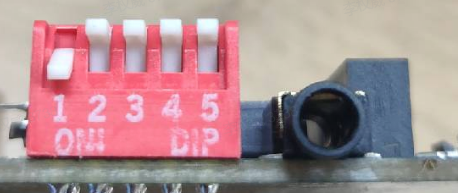

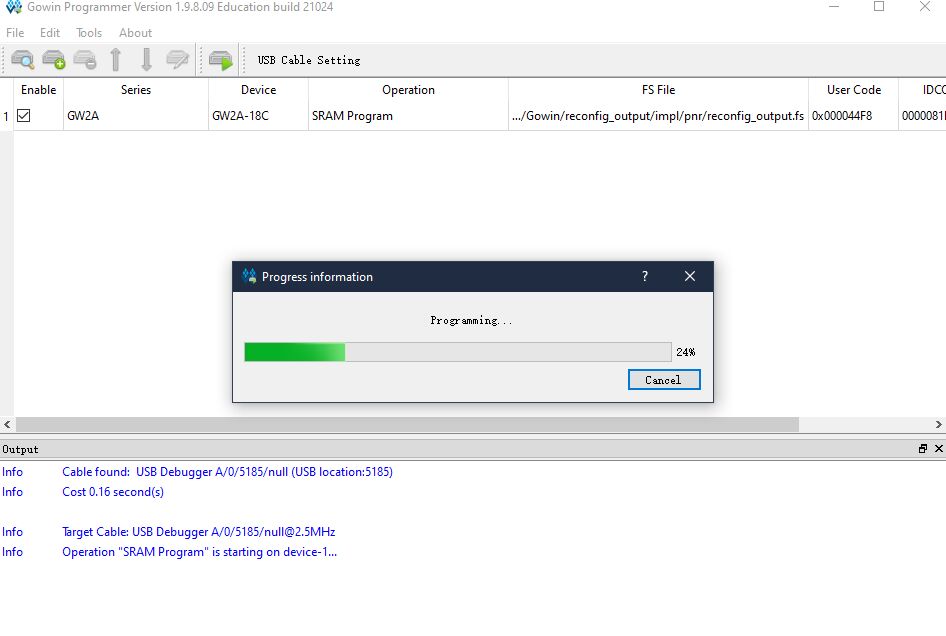

首先正常使能核心板,将拨码开关一号位拨下。然后在 Programmer 软件中,选择一个操作(烧写、擦除都可以),当 Programmer 软件中进度条出现的时候,快速将一号拨码开关拉高,然后再拉低重新使能核心板,这样就会发现 Programmer 可以正常烧录 FPGA 板卡了。

|

首先使能核心板。 |

|

对板卡进行操作,出现进度条的时候快速拨动使能引脚。 |

|

先向上拨动1号拨码开关,再向下拨动 |

|

然后就看到进度条正常,操作顺利 |

中文

中文 Translate

Translate